STS bietet DRC und DFM Service für die Leiterplatte

Printed Circuit Board DRC/DFM Service für Board und Bestückung

Neue Komponenten mit immer mehr Funktionen erhöhen kontinuierlich auch die Menge an Anschlüssen und damit die Anzahl von Lagen und Netzen. Dadurch entstehen immer mehr Regeln, die bei Analysen zur Qualitätssicherung beachtet werden müssen. Wir unterstützen elektronische Entwickler bei einer ihrer Hauptaufgaben, nämlich der Verbesserung der Funktionalität des Produkts, indem wir zeitlichen Spielraum schaffen. Nichtsdestotrotz muss die Herstellung des gesamten Produkts stets überwacht werden.

Die Herausforderung ist, folgende drei Ziele zu vereinen: Verringerung der Time-to-Market, höhere Qualität und Kostenreduzierung. Unser Anliegen ist es, Tools zur Verfügung zu stellen, die die Bare Board Analyse vereinfachen und in der Bestückung volle Unterstützung leisten. Analysen durchzuführen nimmt üblicherweise viel von der Zeit des Entwickler-Teams in Anspruch. Mit unserem DRC/DFM Service können wir diese Zeit zurückgeben.

Was sind die Vorteile eines DRC/DFM Services?

- Zeitersparnis

- Die angewendeten Regeln beruhen auf jahrelanger Erfahrung

- Zusammengefügte Lagen werden zusammen überprüft, um ECAD Exportprobleme zu finden

- Der DRC wird anhand der ausgegebenen Daten durchgeführt, nicht anhand der internen Netzdaten des CAD-Systems

Wir bieten eine Design-Überprüfung umsonst an!

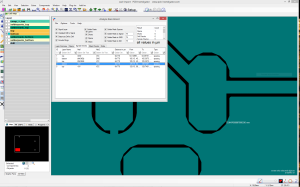

Vollständige Analyse aller Lagen

- Kupferabstände

- Stubs (Bahnen und Bögen laufen ins Leere)

- Abstände zwischen Masken- und Bohrlagen

- Abstände zwischen Masken- und Signallagen

- Abstände zwischen Masken- und SMDs

- Unterbrochene Netze

- Kurzschlüsse

Änderungsverfolgung

- Unterschiede auf allen Leiterplattenlagen

- Unterschiede in Komponenteneigenschaften

- Unterschiede in Netzen

Gegenüberstellung von ODB++ und Gerber Daten

- Unterschiede auf allen Leiterplattenlagen

Gegenüberstellung von ODB++ und IDF 2.0/3.0 Daten

- Unterschiede in Komponenteneigenschaften

Design Übersicht

- Attribute von Lagen und Komponenten

- Lagen Matrix

- Leiterplatten und Nutzenabmessungen

- Leiterplattenattribute

- BOM Informationen

- Bare Board Analyse-Ergebnisse

Test Point Report

- Netzliste mit Anzahl und Position der Testpunkte

Besonderheiten

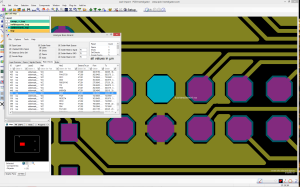

- Komponenten-Analyse für SMD Bestückung

- Tombstone-Analyse für SMD Bestückung

- Gefahrenstellen-Analyse für Netzverfolgung

Jetzt Angebot anfragen

Kontaktieren Sie uns, um ein unverbindliches Angebot

zu dem gewünschten Produkt zu erhalten.